# SEMICONDUCTOR STORAGE DEVICE

Patent Number:

JP63229848

Publication date:

1988-09-26

Inventor(s):

MAEDA SATORU; others: 01

Applicant(s)::

**TOSHIBA CORP**

Requested Patent:

JP63229848

Application Number: JP19870065015 19870319

Priority Number(s):

IPC Classification:

H01L27/10; H01L27/04

EC Classification:

Equivalents:

## **Abstract**

PURPOSE:To prevent the operation speed from decelerating by a method wherein the substrate potential of MOS type transfer gate transistor is raised in case of accumulating data to lower the sub-threshold value leakage current while the substrate potential is lowered in case of a reading/writing process. CONSTITUTION:P wells 12 in the line direction on an n type Si substrate are split by SiO2 layers 13 into memory cells 14. Transfer electrodes and word lines 16 are provided on the regions between capacity electrodes 15, n<-> layers 18 and n<+> layers 19 on the regions 14 using polySi 16. The surface is covered with an SiO2 film 20 and openings 21 are made to provide Al bit lines 17 for connection to pick up layers of P wells 12. The P wells 12 connected to Al wirings 23 through the intermediary of the holes 22 are supplied with the substrate potential. In case of reading/writing process, the P wells in the selected line are supplied with a low substrate potential while in case of accumulating data, the P wells in the selected line are supplied with high substrate potential. Through these procedures, the charge accumulated in capacitors shall not leak through the intermediary of a transfer gate transistor not to erase the data.

Data supplied from the esp@cenet database - I2

## 19 日本国特許庁(JP)

⑩ 特許出願公開

# <sup>®</sup> 公 開 特 許 公 報 (A)

昭63-229848

@Int\_Cl\_1

識別記号

邻出

庁内整理番号

❸公開 昭和63年(1988)9月26日

H 01 L 27/10 27/04

3 2 5

U-8624-5F B-7514-5F

審査請求 有 発明の数 1 (全4頁)

母発明の名称 半導体記憶装置

②特 願 昭62-65015

顋 昭62(1987)3月19日

⑫発 明 者 前 田

哲 神奈川県川崎

哲 神奈川県川崎市幸区小向東芝町1番地 株式会社東芝総合 研究所内

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝総合

研究所内

⑪出 願 人 株式会社東芝

神奈川県川崎市幸区堀川町72番地

邳代 理 人 并理士 鈴江 武彦 外2名

明知書

1. 発明の名称

半導体記憶装置

2. 特許請求の範囲

(1) MOS型転送ゲートトランジスタを有する半導体記憶接蹬において、情報の研出し時もしくは雪込み時に上記MOS型転送ゲートトランジスタの基板電位を後くし、且つ情報の保持状態時には深く設定する基板電位供給手段を設けたことを特徴とする半導体記憶装置。

(2) 前記基板電位は、半導体基板と逆導電型のウェル領域に供給することを特徴とする特許 請求の範囲第1項記載の半導体記憶装置。

(3)前記基板電位は、選択された行または 列のみに選択的に供給することを特徴とする特許 顕求の範囲第1項記載の半導体記憶装置。

3. 発明の詳細な説明

〔発明の目的〕

(産業上の利用分野)

この発明は、半導体記憶装置に関するもので、

特に基板電位の制御に係わる。

(従来の技術)

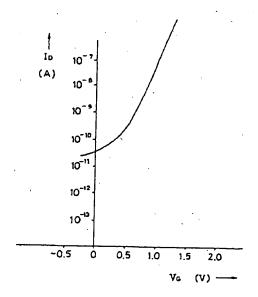

一般に、MOS型転送ゲートトランジスタを 有する半導体記憶装置、例えばダイナミック RAMには基板電位が印加されている。これによ って、ピット線容量の低減、および転送ゲートト ランジスタのサブスレッシュホールドリーク電波 を低減している。しかしなから、各素子の微細化 が進むにつれて転送ゲートトランジスタのチャネ ル長も短くなり(例えばL=Ο、5μm)、現在 使用されている-2V~-3V程度の基板電位で は祭3回に示すようにサブスレッシュホールドリ ーク電流が増加する傾向にある。第3図はMOS 型転送ゲートトランジスタのゲート電圧V。に対 するドレイン電流 Το の特性を示すもので、この リーク電流が増加するとダイナミックRAMの場 合、情報を粛込んでも情報を保持できなくなる。 すなわち、キャパシタに蓄積された電荷が転送ゲ ートトランジスタを介して遊けてしまい、誰込ん だ情報が消えてしまうことになる。このような情

#### ( 発明が解決しようとする問題点)

上述したように従来の半導体記憶接置は、素子の微細化に伴ってサブスレッシュホールドリーク電流が増加し、この電流を低減しようとすると 要込みおよび読出し速度が低下するとともに集子 の劣化を招く欠点がある。

この発明は上記のような事情に扱みてなされたもので、その目的とするところは、書込みおよび

該出し速度の低下や業子の劣化を招くことなくサ

ブスレッシュホールドリーク環境を低減できる半

導体記憶装置を提供することである。

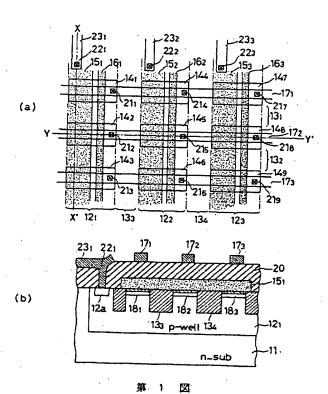

リセルの構成を示すもので、(a)図はパターン 平面図、(b)図は(a)図のX-X「森に沿っ た断面図、(C)図は(a)図のY-Y´稔に沿 った断面図をそれぞれ示している。第1図におい て、11は例えばn型のシリコン基板で、このシリ コン基板 1.1にはD型のウェル領域 1.2』、1.2』、 . 12s が行方向に選択的に形成されている。上記p ウェル領域121 . 122 , 123 には、シリコン酸化 膜から成り列方向に伸びる素子分離領域131. 132、およびシリコン酸化膜から成り行方向に伸 びる案子分離領域13g , 134 が設けられている。 そして、これらの素子分頗領域13』~134 によっ てロウェル領域内にメモリセル領域14』~14』が 形成される。なお、上記列方向に伸びる素子分盤 額域13g . 13g は、(b) 図に示す如く底部が p ウェル領域12の底面(シリコン基板11との境界) より所定の距離だけ隔てられた上方に位置してい る。一方、上記行方向に伸びる素子分離領域133, 134 は、(C)図に示す如く底部がロウェル領域 12の底面に接し、各ウェル領域12』、122、123

#### [発明の偶成]

(問題点を解決するための手段と作用)

すなわち、この発明においては、上記の目的を達成するために、MOS型転送ゲートトランジスタの昼板電位を情報の保持状態時には深くし、情報の製込み時および読出し時にのみ選択的に送くしている。

こうすることにより、MOS型転送ゲートにより、MOS型転送ゲートにより、MOS型転送ゲートにより、MOS型転送ゲートにより、MOS型転送が出る。 いのでサプスレッシュホールドリーク電流をは低いいた。 は、最近のではいるのではないではないになったのではなりをすったのではないのではないのではないのではないのではない。 したのというないのではないのでするというないにないにない。 分にはない。 からない。

#### (実施例)

以下、この発明の一実施例について図面を参照して説明する。第1図(a)~(c)は、この発明をダイナミックRAMに適用した場合のメモ

園も分離している。つまり、メモリセル領域141~143 、144~146 、147~14g はそれぞれ、素子分離領域13g 、134 によって分離されることになる。そして、上記メモリセル領域141~14g および素子分離領域13g 、132 上には、キャバシタ電極15g~15g と例えば多結晶シリコンからなり転送ゲートを兼ねる電極16g~16g が設けられる。すなわち、各メモリセル領域14g~14g 上の電極15g~15g はキャバシタ電極として機能し、n~型拡散層18g~18g とn~型拡散層19g~19g との間の領域上の電板16g~16g は転送ゲート電極およびワードラインとして機能する。

更に、キャパシタ電極15』~15g 上およびゲート電極16」~16g 上を含む全面にシリコン酸化膜からなる層間絶縁膜20が被環形成されている。この層間絶縁膜20には、コンタクトホール21』~21g が開孔されており、この層間絶縁膜20上にアルミ配線(ピットライン)17』~17g が形成され、上記コンタクトホール21』~21g を介してロウェル領域12」、12g の表面領域に設けられた

次に上記のような構成において動作を説明する。まず書込みおよび読出しの場合には、選択された行の基板電位を上記基板電位発生回路の出力によって浅く設定する。例えば p ウェル領域 12』にアルミ配線 23』を介して例えば - 2 V の基板電位を与える。この時、転送ゲートトランジスタのサブ

MOS型転送ゲートトランジスタの基板電位は情報の保持時には深いのでサアスレッシュホールドジーク電流を低減できる。しかも、情報の強いないのでからない。このトランジスを変成が低下することはなく、このトランジスををすってもあるにゲートに高電圧を印加する必要はないのでゲート酸化膜の破壊や素子の劣化等を防止できる。

### [ 発明の効果]

以上説明したようにこの発明によれば、書込みおよび読出し速度の低下や素子の劣化を招くことなくサプスレッシュホールドリーク電流を低減できる半導体記憶装置が得られる。

#### 4. 図面の原単な説明

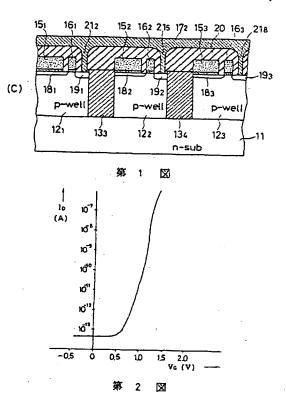

第1図はこの発明の一実施院に係わる半導体 記憶装置について説明するための図、第2図は上 記第1図の装置におけるサブスレッシュホールド リーク電流特性を示す図、第3図は従来の半導体 記憶装置におけるサブスレッシュホールドリーク 電流特性を示す図である。 次に、情報をキャパシタに保持する(非選択)は、選択された行のロウェル領域に例えば一ち、選択された行のロウェル領域にので、はいる。これによったのをでは新2回に示すようになり、ン・サーク電圧V。が0Vの時には、この電波は1、メートの1・「A」程度に押えられる。従ってラマを関してきる。

このような構成によれば、上述したように

11…シリコン基板、12』~123 … ウェル領域、131~134 … 素子分離領域、141~14g … メモリセル領域。

出願人代理人 弁理士 鈴江武彦

## 特開昭63-229848(4)

第 3 図

- (19) Japanese Patent Office (JP)

- (12) Patent Publication (A)

- (11) Japanese Patent Provisional Publication of a patent application No. Sho 63-229848

- (43) Publication: September 26, Showa 63 (1988)

- (51) Int.Cl. 4 Identification Internal

- H 01 L 27/10 Symbol Reference No. 27/04 325 U-8624-5F

B-7514-5F

Request for Examination: requested Number of invention(s) 1 (Total 4 pages)

- (54) Title of the Invention: Semiconductor Storage Device

- (21) Application No. Patent Application Sho 62-65015

- (22) Filing date March 19 Showa 62 (1987)

- (72) Inventor: Maeda Satoru

c/o Research and Development Center,

Toshiba Corporation

1, Komukai-Toshiba-cho, Saiwai-ku,

Kawasaki-shi, Kanagawa-ken, Japan

(72) Inventor: Iwai Hiroshi

c/o Research and Development Center,

Toshiba Corporation

1, Komukai-Toshiba-cho, Saiwai-ku,

Kawasaki-shi, Kanagawa-ken, Japan

(71) Applicant: Toshiba Corporation

72, Horikawa-cho, Saiwai-ku,

Kawasaki-shi, Kanagawa-ken, Japan

(74) Agent Suzue Takehiko, Patent Attorney

And other 2 agents

## SPECIFICATION

1. Title of the Invention

Semiconductor Storage Device

# 2. What Is Claimed Is

- (1) A semiconductor storage device having a MOS type transfer gate transistor, comprising substrate potential supply means for, upon information reading or writing, setting the substrate potential of the MOS transfer gate transistor to be shallow, and in information hold status, setting the substrate potential to be deep.

- (2) The semiconductor storage device according to claim 1, wherein said substrate potential is supplied to a well region of inverse conductive type to the semiconductor substrate.

- (3) The semiconductor storage device according to claim 1, wherein said substrate potential is selectively supplied only to a selected row or column.

- 3. Detailed Description of the Invention

[Purpose of the Invention]

(Industrial Field of Utilization)

This invention relates to a semiconductor storage device, and more particularly, to a substrate potential control.

(Conventional Art)

Generally, a substrate potential is applied to a semiconductor storage device having an MOS transfer gate transistor such as a dynamic RAM, thereby a bit line capacity

is reduced, and subthreshold leak current of the transfer gate transistor is reduced. However, as the respective devices become fine, the channel length of the transfer gate transistor becomes shorter (for example, L=0.5  $\mu m)\,.$  At the currently used -2V to -3V substrate potential, the subthreshold leak current tends to increase as shown in Fig. 3. Figs. 3 shows the characteristic of drain current  $I_{\scriptscriptstyle \rm D}$  with respect to gate voltage  $V_{\mbox{\tiny $\mathrm{i}$}}$  of the MOS transfer gate transistor. In use of dynamic RAM, when the leak current increases, even if information is written, the information cannot be held. That is, electric charge accustomed in the capacitor moves out via the transfer gate transistor and the written information is lost. To prevent such information loss, the substrate potential may be deeper (for example, -5V) than the conventional potential, however, the setting of the substrate potential to be deep (low), it is necessary to apply a high voltage to the gate to turn the transfer gate transistor on, and the speed of writing and reading is reduced. Further, when the high voltage is applied to the gate of the transfer gate transistor, a high electric field is applied to the transistor, and the gate oxide film may be easily broken or the device is degraded.

(Problem That the Invention Is to Solve)

As described above, in the conventional semiconductor storage device, as the devices become fine, the subthreshold

leak current increases, and when the current is reduced, the speed of writing and reading is lowered, and the device may be degraded.

The present invention has been made in view of the above situation, and has its object to provide a semiconductor storage device in which the subthreshold leak current can be reduced without reduction of writing and reading speed and device degradation.

[Construction of the Invention]

(Means for Solving the Problem and Operation)

That is, in the present invention, to attain the above object, the substrate potential of MOS transfer gate transistor is set to be deep in information holding status, and selectively set to be shallow only upon information writing and reading.

In this arrangement, as the substrate potential of the MOS transfer gate transistor is deep when information is held, the subthreshold leak current can be reduced, and as the potential is shallow when information is written and read, the operation speed is not lowered. Further, it is not necessary to apply a high voltage to the gate to turn the transistor on, there is no possibility that the device is degraded and the gate oxide film is easily broken.

(Working Example)

Hereinbelow, a working example of the present

invention will be described with reference to the drawings. Figs. 1(a) to (c) show the construction of memory cell in the case where the present invention is applied to a dynamic RAM. (a) is a pattern flat view; (b), a cross-sectional view along a line X-X' in Fig. (a); and (c), a cross-sectional view along a line Y-Y' in Fig. (a). In Fig. 1, numeral 11 denotes a silicon substrate of e.g. n type. On the silicon substrate 11, p-type well regions  $12_1$ ,  $12_2$ ,  $12_3$  are selectively formed in a row direction. in the p well regions  $12_1$ ,  $12_2$ ,  $12_3$ , device isolation regions  $13_1$ ,  $13_2$  of silicon oxide film, extending in a column direction, and device isolation regions  $13_3$ ,  $13_4$  of silicon oxide film, extending in the row direction, are formed. Memory cell regions  $14_{\scriptscriptstyle 1}$ to  $14_{\,9}$  are formed in the p well regions by these device isolation regions 13; to 13. Note that bottoms of the device isolation regions  $13_1$  and  $13_2$  extending in the column direction are in upper positions away from the bottom surfaces of the p well regions 12 (boundary from the silicon substrate 11) by a predetermined distance, as shown in Fig. (b). On the other hand, bottoms the device isolation regions  $13_3$ ,  $13_4$  extending the row direction are in contact with the bottom surfaces of the p well regions 12 as shown in Fig. (c), and the respective well regions  $12_1,\ 12_1,\ 12_3$  are away from each other. That is, the memory cell regions  $14_1\ \text{to}$  $14_3$ ,  $14_4$  to  $14_6$ ,  $14_7$  to  $14_9$  are respectively isolated by the

device isolation regions  $13_3$ ,  $13_4$ . Capacitor electrodes  $15_1$  to  $15_3$  and electrodes  $16_1$  to  $16_3$  of e.g. polycrystalline silicon which serve as transfer gates, are provided on the memory cell regions  $14_1$  to  $14_4$  and the device separation regions  $13_1$ ,  $13_2$ . That is, the electrodes  $15_1$  to  $15_3$  on the respective memory cell regions  $14_1$  to  $14_4$  function as capacitor electrodes, and the electrodes  $16_1$  to  $16_3$  on regions between the  $n^-$  diffusion layers  $18_1$  to  $18_3$  and  $n^+$  diffusion layers  $19_1$  to  $19_3$  function as the transfer gate electrodes and word lines.

Further, an interlayer insulating film 20 of silicon oxide film is formed over the entire surface including the upper surfaces of the capacitor electrodes 15, to 15, and the gate electrodes 16, to 16. The interlayer insulating film 20 has contact holes 21, to 21, and aluminum wires (bit lines) 17, to 17, are formed on the interlayer insulating film 20, and connected via the contact holes 21, to 21, to a high concentration p<sup>+</sup> impurity region 12a provided in surface regions of the p well regions 12, 12, 12, Eurther, contact holes 22, to 22, for application of substrate potential are formed in the p well regions 12, to 12, and connected via aluminum wires 23, to 23, to a substrate potential generation circuit (substrate potential supply means) (not shown). Upon information reading or writing, the substrate potential generation circuit supplies a

potential at e.g. -2 V to -3 V to the p well region where a selected transfer gate transistor is formed, and supplies e.g. -5 V to the p well region where the transfer gate transistor of unselected memory cell is formed. On the other hand, in information holding status, the circuit supplies e.g. -5 V to all the p well regions  $12_1$  to  $12_3$ .

Next, the operation in the above construction will be described. First, in writing and reading, the substrate potential of selected row is set to be shallow by the output from the substrate potential generation circuit. example, the substrate potential at e.g. -2 V is applied to the p well region  $12_1$  via the aluminum wire  $23_1$ . At this time, the characteristic of the subthreshold leak current of the transfer gate transistor is as shown in Fig. 3. Even when the gate voltage  $V_{\text{G}}$  is 0V, the current flows, and the transfer gate transistor becomes on status. Accordingly, it is not necessary to apply a high voltage to the gate electrode, thus breakage of gate oxide film due to device degradation can be prevented. Note that at this time, the lead current flows, however, upon writing, even if some leak current exists, refresh (rewrite) is performed, therefore, there is no problem.

Next, in a case where information is held in the capacitor (non-selection), the substrate potential at e.g. -5 V is applied to the p well region of the selected row.

By this arrangement, the characteristic of the subthreshold leak current of the transfer gate transistor is as shown in Fig. 2. When the gate voltage  $V_G$  is 0V, the current is suppressed to about  $1\times10^{-14}$  [A]. Accordingly, the leakage of the electric charge accumulated in the capacitor via the transfer gate transistor and loss of written information can be prevented.

In accordance with the construction, as described above, as the substrate potential of MOS transfer gate transistor is deep when information is held, the subthreshold leak current can be reduced. Further, upon information writing and reading, as the potential is shallow, the access speed is not lowered. As it is not necessary to apply a high voltage to the gate to turn the transistor on, the breakage of gate oxide film and device degradation can be prevented.

[Effect of the Invention]

As described above, according to the present invention, a semiconductor storage device which enables reduction of subthreshold leak current without reduction of the speed of writing and reading and device degradation can be obtained.

# 4. Brief Description of the Drawings

Fig. 1 is a diagram explaining the one semiconductor storage device according to the working example of the present invention; Fig. 2, a diagram showing the

-9-

characteristic of subthreshold leak current in the device in Fig. 1; and Fig. 3, a diagram showing the characteristic of subthreshold leak current in the conventional semiconductor storage device.

11 ... silicon substrate, 12 $_1$  to 12 $_3$  ... well region, 13 $_1$  to 13 $_4$  ... device separation region, 14 $_1$  to 14 $_9$  ... memory cell region.

Agent: Suzue Takehiko, Patent Attorney